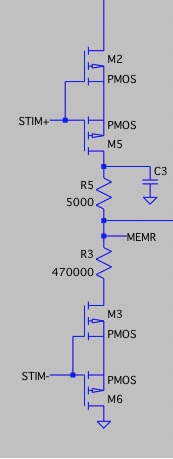

Back to Back MOSFET topology

The topology can be used as illustrated from top & bottom of the memristor ( Crossbar application) or only on top ( simple application like SOAP project). The current limitation resistor and a decoupling capacitor are included. The main problem with the B2B stage is the precise MOSFET point of commutation that will be fully covered by the FPGA. For the illustration of the simulation, we used a resistor of 470K instead of complex memristor model. 470K is the worst case value for timing performance.

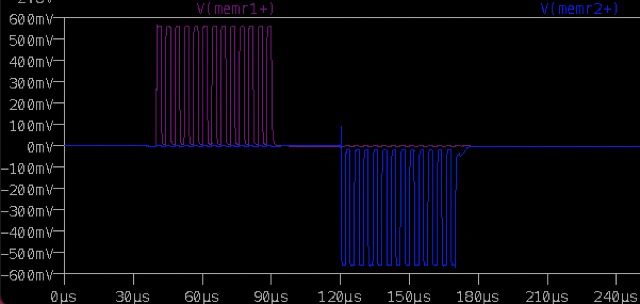

The figure shows a simulation plot under LTSPICE & highlights the timing performance of the stage ( pulses of 2us , but can be lowered to 500ns ). Positive pulses on Memristor 1 ( programming ) Negative pulses of Memristors 2 (Erasing)

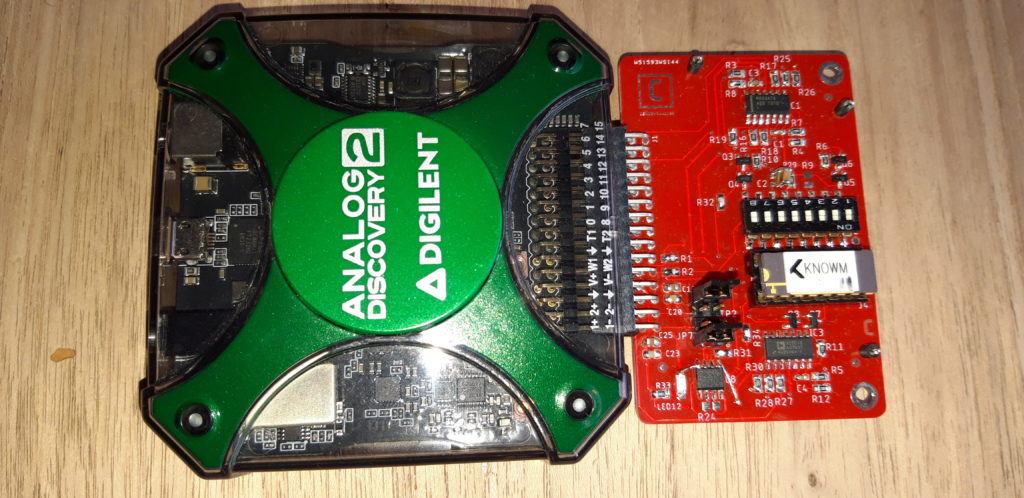

The back to back topology can be evaluated with a dedicated board ( AD2 compatible )

In case your are interested by having this boards for investigation don’t hesitate to contact us for a quotation.

JP Guarrera – Manager & Principal Engineer jp.guarrera@conceptualise.be